## September 13, 2007

# FN7325.11

# *Triple Differential Twisted-Pair Driver with Common-Mode Sync Encoding*

intercil

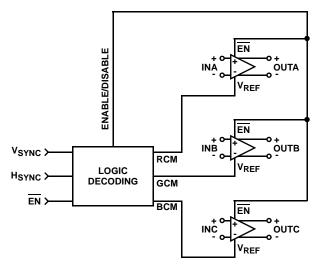

The EL4543 is a high bandwidth triple differential amplifier with integrated encoding of video sync signals. The inputs are suitable for handling high speed video or other communications signals in either single-ended or differential form, and the common-mode input range extends all the way to the negative rail enabling ground-referenced signalling in single supply applications. The high bandwidth enables differential signalling onto standard twisted-pair or coax with very low harmonic distortion, while internal feedback ensures balanced gain and phase at the outputs reducing radiated EMI and harmonics.

Embedded logic encodes standard video horizontal and vertical sync signals onto the common mode of the twisted pair(s), transmitting this additional information without the requirement for additional buffers or transmission lines. The EL4543 enables significant system cost savings when compared with discrete line driver alternatives.

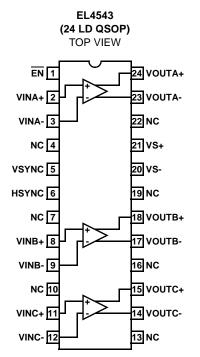

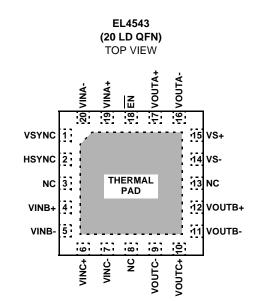

The EL4543 is available in both a 24 Ld QSOP package and a 20 Ld QFN package and is specified for operation over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

| н    | v    | COMMON<br>MODE A<br>(RED) | COMMON<br>MODE B<br>(GREEN) | COMMON<br>MODE C<br>(BLUE) |  |

|------|------|---------------------------|-----------------------------|----------------------------|--|

| Low  | High | 3.0                       | 2.0                         | 2.5                        |  |

| Low  | Low  | 2.5                       | 3.0                         | 2.0                        |  |

| High | Low  | 2.0                       | 3.0                         | 2.5                        |  |

| High | High | 2.5                       | 2.0                         | 3.0                        |  |

## TABLE 1. SYNC SIGNAL ENCODING

## TABLE 2. INPUT LOGIC THRESHOLD (+5V SUPPLY)

| V <sub>LO</sub> , max | 0.8V |  |  |

|-----------------------|------|--|--|

| V <sub>HI</sub> , min | 2V   |  |  |

# Features

- Fully differential inputs, outputs, and feedback

- 350MHz -3dB bandwidth

- 1200V/µs slew rate

- -75dB distortion at 5MHz

- Single 5V to 12V operation

- 50mA minimum output current

- Low power 36mA total typical supply current

- Pb-free available (RoHS compliant)

# Applications

- Twisted-pair drivers

- Differential line drivers

- VGA over twisted-pair

- · Transmission of analog signals in a noisy environment

# **Ordering Information**

| PART<br>NUMBER                | PART<br>MARKING | PACKAGE                     | PKG.<br>DWG. # |

|-------------------------------|-----------------|-----------------------------|----------------|

| EL4543IU                      | EL4543IU        | 24 Ld QSOP                  | MDP0040        |

| EL4543IU-T7**                 | EL4543IU        | 24 Ld QSOP                  | MDP0040        |

| EL4543IU-T13**                | EL4543IU        | 24 Ld QSOP                  | MDP0040        |

| EL4543IUZ<br>(See Note)       | EL4543IUZ       | 24 Ld QSOP<br>(Pb-free)     | MDP0040        |

| EL4543IUZ-T7**<br>(See Note)  | EL4543IUZ       | 24 Ld QSOP<br>(Pb-free)     | MDP0040        |

| EL4543IUZ-T13**<br>(See Note) | EL4543IUZ       | 24 Ld QSOP<br>(Pb-free)     | MDP0040        |

| EL4543IL                      | 4543IL          | 20 Ld 4x4 QFN*              | L20.4x4B       |

| EL4543IL-T7**                 | 4543IL          | 20 Ld 4x4 QFN*              | L20.4x4B       |

| EL4543IL-T13**                | 4543IL          | 20 Ld 4x4 QFN*              | L20.4x4B       |

| EL4543ILZ<br>(See Note)       | 4543ILZ         | 20 Ld 4x4 QFN*<br>(Pb-free) | L20.4x4B       |

| EL4543ILZ-T7**<br>(See Note)  | 4543ILZ         | 20 Ld 4x4 QFN*<br>(Pb-free) | L20.4x4B       |

| EL4543ILZ-T13**<br>(See Note) | 4543ILZ         | 20 Ld 4x4 QFN*<br>(Pb-free) | L20.4x4B       |

\*20 Ld 4x4 QFN, exposed pad 2.7 x 2.7mm is connected to  $\rm V_{S}\textsc{-}$

\*\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Absolute Maximum Ratings (T<sub>A</sub> = +25°C)

| Supply Voltage (V <sub>S</sub> + & V <sub>S</sub> -)+12\ | / |

|----------------------------------------------------------|---|

| Maximum Output Continuous Current ±70m/                  | ł |

| Storage Temperature Range65°C to +150°C                  | 2 |

| Operating Junction Temperature+135°C                     | 2 |

| Ambient Operating Temperature40°C to +85°C                           |

|----------------------------------------------------------------------|

| $V_{IN+}$ , $V_{INB}$ $V_{S-} + 0.8V$ (min) to $V_{S+} - 0.8V$ (max) |

| V <sub>IN</sub> V <sub>INB</sub> ±5V                                 |

| Pb-free reflow profilesee link below                                 |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp                     |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

#### **Electrical Specifications** $V_S$ + = +5V, $V_S$ - = 0V, $T_A$ = +25°C, $V_{IN}$ = 0V, $R_L$ = 150 $\Omega$ , unless otherwise specified.

| PARAMETER           | DESCRIPTION                                               | CONDITIONS                                                                     | MIN<br>(Note 1) | TYP   | MAX<br>(Note 1) | UNIT   |

|---------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|-----------------|-------|-----------------|--------|

| AC PERFORMA         | ANCE                                                      |                                                                                | J               |       | 1               |        |

| BW (-3dB)           | -3dB Bandwidth                                            | V <sub>OUT</sub> = 2V <sub>P-P</sub>                                           |                 | 350   |                 | MHz    |

| SR                  | Differential Slew Rate                                    | $R_L = 200\Omega$                                                              | 600             | 1000  |                 | V/µs   |

| T <sub>STL</sub>    | Settling Time to 0.1%                                     |                                                                                |                 | 13.6  |                 | ns     |

| GBW                 | Gain Bandwidth Product                                    |                                                                                |                 | 700   |                 | MHz    |

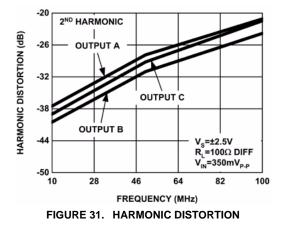

| HD2                 | 2nd Harmonic Distortion                                   | $f = 20MHz, R_L = 200\Omega$                                                   |                 | -70   |                 | dBc    |

| HD3                 | 3rd Harmonic Distortion                                   | $f = 20MHz, R_L = 200\Omega$                                                   |                 | -70   |                 | dBc    |

| dP                  | Differential Phase @ 3.58MHz                              |                                                                                |                 | 0.01  |                 | ۰      |

| dG                  | Differential Gain @ 3.58MHz                               |                                                                                |                 | 0.01  |                 | %      |

| INPUT CHARAG        | CTERISTICS                                                |                                                                                |                 |       |                 | 1      |

| V <sub>OS</sub>     | Input Referred Offset Voltage                             |                                                                                | -10             | 2     | 10              | mV     |

| I <sub>IN</sub>     | Input Bias Current (V <sub>IN</sub> +, V <sub>IN</sub> +) |                                                                                | -30             | -15   | -10             | μA     |

| Z <sub>IN</sub>     | Differential Input Impedance                              |                                                                                |                 | 180   |                 | kΩ     |

| C <sub>IN</sub>     | Input Capacitance                                         | Capacitance between any single input pin and the power supplies                |                 | 4     |                 | pF     |

| V <sub>DIFF</sub>   | Differential Input Range                                  |                                                                                |                 | ±0.75 |                 | V      |

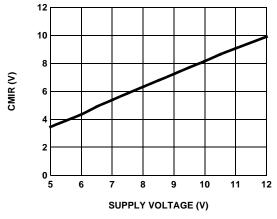

| V <sub>CM</sub>     | Input Common Mode Voltage Range                           | $V_{S}$ + = +5V, $V_{S}$ - = 0V.<br>See Figure 7 for higher supply voltages.   | 0               |       | 2.3             | V      |

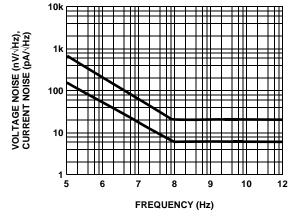

| V <sub>N</sub>      | Input Referred Voltage Noise                              |                                                                                |                 | 27    |                 | nV/√Hz |

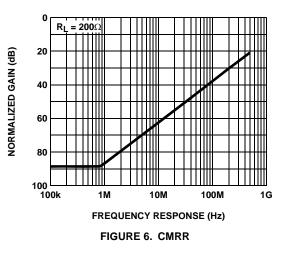

| CMRR                | Input Common Mode Rejection Ratio                         | $V_{CM} = 0$ to 2V                                                             | 60              | 80    |                 | dB     |

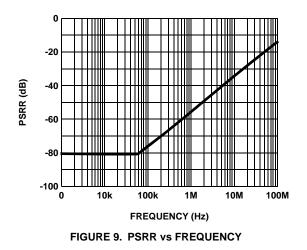

| EN                  | Threshold                                                 |                                                                                |                 | 1.4   |                 | V      |

| OUTPUT CHAR         | ACTERISTICS                                               |                                                                                |                 |       |                 |        |

| IOUT                | Output Peak Current                                       |                                                                                | 40              | 60    |                 | mA     |

| C <sub>OUT</sub>    | Output Capacitance (Disabled)                             | Capacitance between any single output pin and the power supplies when disabled |                 | 12    |                 | pF     |

| DC PERFORMA         | ANCE                                                      |                                                                                |                 |       |                 |        |

| A <sub>V</sub>      | Voltage Gain                                              | $V_{IN} = 0.8V_{P-P}$                                                          | 1.82            | 1.96  | 2.05            | V/V    |

| SUPPLY CHAR         | ACTERISTICS                                               |                                                                                |                 |       | ·               |        |

| V <sub>SUPPLY</sub> | Supply Operating Range                                    | $V_{S}$ + to $V_{S}$ -                                                         | 5               |       | 12              | V      |

| I <sub>S</sub>      | Power Supply Current (per Channel)                        |                                                                                | 12.3            | 14.5  | 16.2            | mA     |

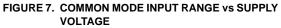

| PSRR                | Power Supply Rejection Ratio                              |                                                                                | 70              | 80    |                 | dB     |

NOTE:

1. Parts are 100% tested at +25°C. Over-temperature limits established by characterization and are not production tested.

# **Pin Descriptions**

| QFN<br>PIN NUMBER  | QSOP<br>PIN NUMBER          | PIN NAME | PIN DESCRIPTION                   | EQUIVALENT CIRCUIT           |

|--------------------|-----------------------------|----------|-----------------------------------|------------------------------|

| 18                 | 1                           | ĒN       | Disables video inputs and outputs |                              |

| 19                 | 2                           | VINA+    | Non-inventing input               |                              |

| 20                 | 3                           | VINA-    | Inverting input                   |                              |

| 3, 8, 13           | 4, 7, 10, 13,<br>16, 19, 22 | NC       | Not connected                     |                              |

| 1                  | 5                           | VSYNC    | Vertical sync logic input         | V <sub>SM</sub><br>CIRCUIT 2 |

| 2                  | 6                           | HSYNC    | Horizontal sync logic input       | Reference Circuit 2          |

| 4                  | 8                           | VINB+    | Non-inverting input               |                              |

| 5                  | 9                           | VINB-    | Inverting input                   |                              |

| 6                  | 11                          | VINC+    | Non-inverting input               |                              |

| 7                  | 12                          | VINC-    | Inverting input                   |                              |

| 9                  | 14                          | VOUTC-   | Inverting output                  |                              |

| 10                 | 15                          | VOUTC+   | Non-inverting output              |                              |

| 11                 | 17                          | VOUTB-   | Inverting output                  |                              |

| 12                 | 18                          | VOUTB+   | Non-inverting output              |                              |

| 14, Thermal<br>Pad | 20                          | VS-      | Negative supply                   |                              |

| 15                 | 21                          | VS+      | Positive supply                   |                              |

| 16                 | 23                          | VOUTA-   | Non-inverting output              |                              |

| 17                 | 24                          | VOUTA+   | Inverting output                  |                              |

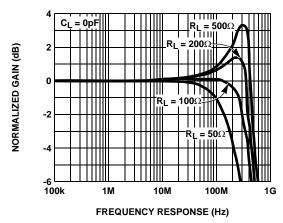

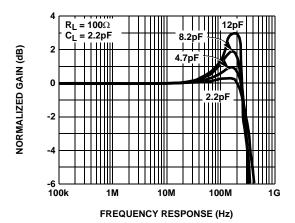

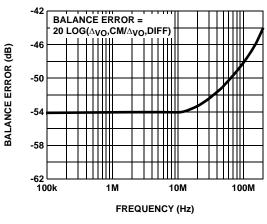

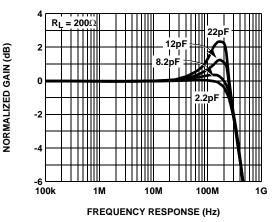

# **Typical Performance Curves**

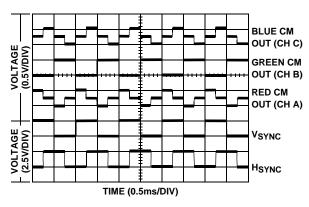

FIGURE 1. COMMON MODE OUTPUT

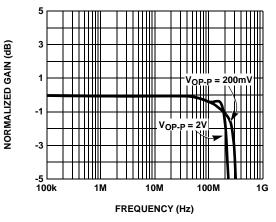

FIGURE 3. DIFFERENTIAL FREQUENCY RESPONSE FOR VARIOUS  $\rm R_L$  - DIFF

FIGURE 5. DIFFERENTIAL FREQUENCY RESPONSE FOR VARIOUS  $C_L$  - DIFF

FIGURE 2. BALANCE ERROR

FIGURE 4. DIFFFERENTIAL FREQUENCY RESPONSE FOR VARIOUS CL - DIFF

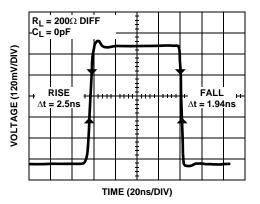

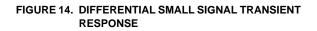

FIGURE 15. DIFFERENTIAL LARGE SIGNAL TRANSIENT RESPONSE

7

int<u>er</u>sil

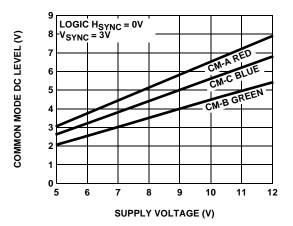

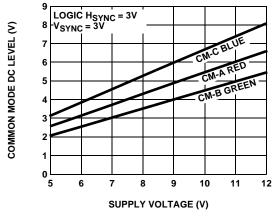

FIGURE 16. COMMON MODE DC LEVEL vs SUPPLY VOLTAGE

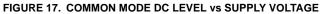

FIGURE 18. COMMON MODE DC LEVEL vs SUPPLY VOLTAGE

FN7325.11 September 13, 2007

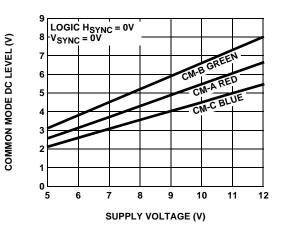

FIGURE 19. COMMON MODE DC LEVEL vs SUPPLY VOLTAGE

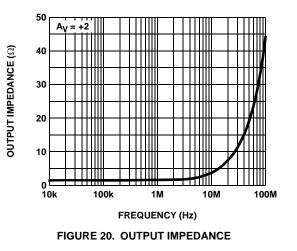

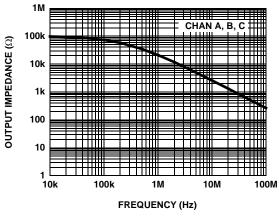

FIGURE 21. OUTPUT IMPEDANCE [DISABLED]

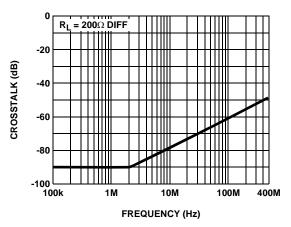

FIGURE 22. CHANNEL ISOLATION vs FREQUENCY

OUTPUT C-

100M

1G

IIIN

OUTPUT C+

FREQUENCY (Hz)

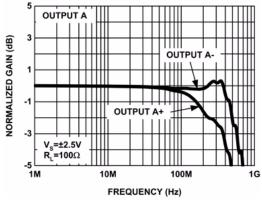

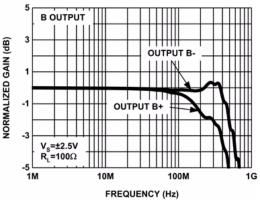

FIGURE 27. GAIN vs FREQUENCY - 2 CHANNELS

10M

FIGURE 25. GAIN vs FREQUENCY - 2 CHANNELS

5

3

1

-1

-3

-5∟ 1M

NORMALIZED GAIN (dB)

C OUTPUT

V<sub>s</sub>=±2.5V

R\_=100Ω

FIGURE 26. GAIN vs FREQUENCY - 2 CHANNELS

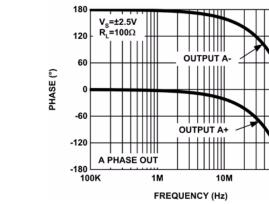

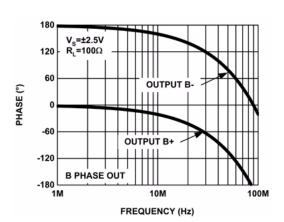

FIGURE 29. PHASE vs FREQUENCY - 2 CHANNELS

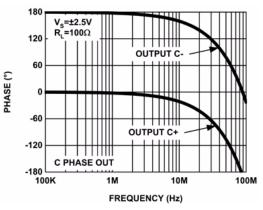

FIGURE 30. PHASE vs FREQUENCY - 2 CHANNELS

100M

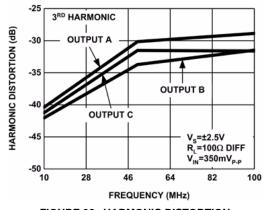

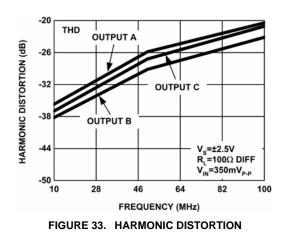

**FIGURE 32. HARMONIC DISTORTION**

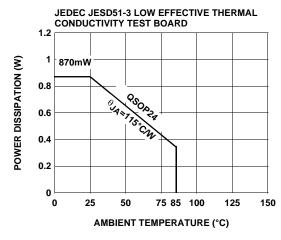

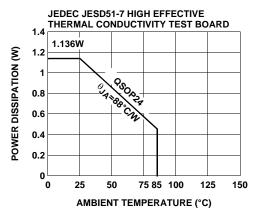

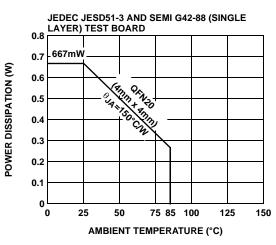

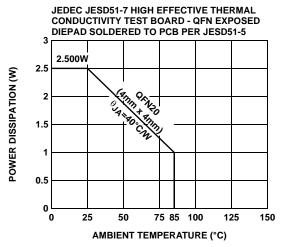

FIGURE 35. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

FIGURE 34. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

FIGURE 37. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

# **Operational Description and Application** Information

## Introduction

The EL4543 is designed to differentially drive composite RGB video signals onto twisted pair lines, while simultaneously encoding horizontal and vertical sync signals as common mode output. The entire video signal plus sync can therefore be transmitted on 3 twisted pairs of wire. When utilizing CAT5 cable, the 4th available twisted pair can be used for transmission of audio, data or control information. The distribution of composite video over standard CAT5 cable enables enormous cost and labor savings compared with traditional coaxial cable, when considering both the relative low price and ease of pulling CAT5 cable.

## Functional Description

The EL4543 provides three fully differential high-speed amplifiers, suitable for driving high-resolution composite video signals onto twisted pair or standard coaxial cable. The input common-mode range extends to the negative rail, allowing simple ground-referenced input termination to be used with a single supply. The amplifiers provide a fixed gain of +2 to compensate for standard video cable termination schemes. Horizontal and Vertical sync signals (HSYNC and V<sub>SYNC</sub>) are passed to an internal Logic Encoding Block to encode the sync information as three discrete signals of different voltage levels. Generally, in differential amplifiers an external V<sub>RFF</sub> pin is used to control the common mode level of the differential output; in the case of the EL4543 the V<sub>RFF</sub> of each of the three internal amplifier channels receives a signal from the Logic Encoding Block with encoded HSYNC and VSYNC information. The final output consists of three fully differential video signals, with sync encoded on the common mode of each of the three RGB differential signals. H<sub>SYNC</sub> and V<sub>SYNC</sub> can easily be separated from the

differential output signals, decoded and transmitted along with the RGB video signals to the video monitor.

# Sync Transmission

The EL4543 encodes H<sub>SYNC</sub> and V<sub>SYNC</sub> signals on the common mode output of the differential video signals; Red, Green and Blue respectively. Data Sheet Figures 16, 17 and 18 clearly illustrate that the sum of the common mode voltages results in a fixed average DC level with no AC content and illustrates the logic levels. This eliminates EMI radiation into any common mode signal along the twisted pairs of CAT5 cable.

# Extract Common Mode Sync and Decode $H_{SYNC}$ and $V_{SYNC}$

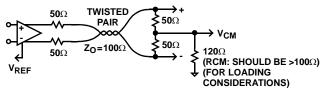

$H_{SYNC}$  and  $V_{SYNC}$  can be regenerated from the Common Mode sync output voltages. The relationships between  $H_{SYNC}$ ,  $V_{SYNC}$  and the 3 common mode levels are given by Table 1. The common mode levels are easily separated from the differential outputs of the EL4543 using this simple resistor network at the cable receiver input of each differential channel; see Figure 39.

## Twisted Pair Termination

The schematic in Figure 39 illustrates a termination scheme for  $50\Omega$  series termination and a  $100\Omega$  twisted pair cable. Note RCM is the common mode termination to allow measurement of  $V_{CM}$  and should not be too small since it loads the EL4543; a little over a  $100\Omega$  is recommended for RCM.

#### TYPICAL EL4543 TERMINATION DRIVER

## Video Transmission

The EL4543 is a twisted pair differential line driver directed at the transmission of Video Signals through cables up to 100 feet; however, as signal losses increase with transmission line length the EL4543 will need additional support to equalize video signals along longer twisted pair transmission lines. A full solution to accomplish this is the SXGA Video Transmission System presented in the EL4543 Data Sheet. Note the inclusion of the EL9110 for signal equalization of up to 1000ft of CAT5 cable and common mode extraction; see Data Sheet for additional information on the EL9110.

# Long Distance Video Transmission

The SXGA Video Transmission System makes it possible to transmit Red, Green and Blue (RGB) video plus sync up to 1000 feet through CAT5 cable. The input to the SXGA Video Transmission System is the output of a video source transmitting RGB video signals plus sync. The signals are received initially by the EL4543; which converts the single ended input RGB signals to three fully differential waveforms with sync encoded on the discrete common modes of each color channel and then drives the signals through a length of CAT5 cable. The signal is received by the EL9110, which can provide 6-pole equalization for both high and low frequency signal transmission line losses. Then the EL9110 converts the differential RGB video signals back into single ended format while extracting the common mode component for decoding. The single ended RGB signal is taken directly from the output of the El9110 and is ready for the output device. The Common Mode Decoder Circuit receives the common mode signals directly from each of the three

EL9110's common mode output pin, decodes and transmits  $H_{SYNC}$  and  $V_{SYNC}$  to the output device.

## Sync Transmission

The EL4543 encodes  $H_{SYNC}$  and  $V_{SYNC}$  signals onto the common mode output of the differential video signals; Red, Green and Blue respectively. Data Sheet Figure 8 clearly illustrates that the sum of the common mode voltages results in a fixed DC level with no AC content; thus eliminating EMI interference.

## **Output Drive Protection**

The EL4543 has internal short circuit protection set typically at 60mA. if the output is shorted for extended periods of time the increased power dissipation will eventually destroy the part. To realize maximum reliability the output current should never exceed 60mA. The  $50\Omega$  series back load matching resistor provides additional protection.

## Supply Voltage

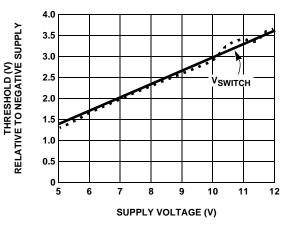

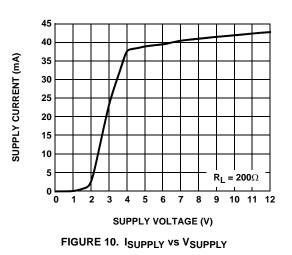

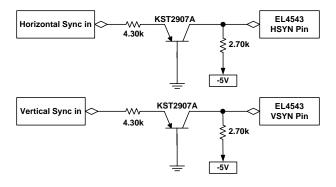

While the EL4543 can be operated on ±5V split rails, single supply 0V to 5V is the most common usage. It is very important to note that the input logic thresholds are relative to the negative supply pin, and therefore single supply, ground referenced logic will not work when driving the EL4543 on split rails. The amplifiers have an input common mode range from 0V to 2.3V with a 0V to 5V supply, increasing with supply voltage (see Figure 7). The common mode output DC level range is a linear function of the power supply (see Figures 16, 17, 18, and 19). The common mode input switching threshold as well as the Enable/Disable input is a linear function of the supply voltage (see Figures 8 and 11). In the event that the EL4543 is to be used with ±5V split rails then the input sync signals need to be voltage offset before they are input to the EL4543. The circuit configuration depicted in Figure 40 provides for the proper level shift.

#### FIGURE 40. LEVEL SHIFTING SYNC SIGNALS FOR USE WITH ±5V SPLIT RAILS

## Disable and Power Down

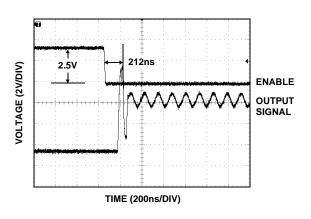

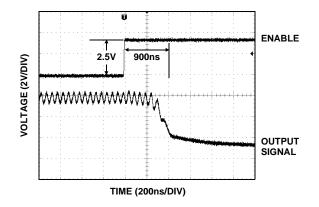

The EL4543 provides an enable disable function which powers down, logic input high, in 900ns and powers up, logic input low, in 212ns. Disabled the amplifiers supply current is reduced to 1.8mA (Positive Supply) and 0mA (Negative Supply). Note that Enable/Disable threshold is a linear function of the supply voltage levels. The Enable/Disable threshold voltage level is compatible with standard TTL/CMOS and referenced to the lowest supply potential.

## Proper Layout Technique

A critical concern with any PCB layout is the establishment of a "healthy" ground plane. It is imperative to provide ground planes terminated close to inputs to minimize input capacitance. Additionally, the ground plane can be selectively removed from inputs to prevent load and supply currents from flowing near the input nodes.

In general the following guidelines apply to all PCB layout:

- Keep all traces as short as possible.

- Keep power supply bypass components as close to the chip as possible extremely close.

- Create a healthy ground with low impedance and continuous ground pathways available to all grounded components board-wide.

- In high frequency applications on multi-level boards try to keep one level of board with continuous ground plane and minimum via cutouts providing it is affordable.

- Provide extremely short loops from power pin to ground.

- If it is affordable, a ferrite bead is always of benefit to isolate device from Power Supply noise and the rest of the circuit from the noise of the device.

# Power Dissipation Calculation

When switching at high speeds, or driving heavy loads, the EL4543 drive capability is ultimately limited by the rise in die temperature brought about by internal power dissipation. For reliable operation die temperature must be kept below  $T_{JMAX}$  (125°C). It is necessary to calculate the power dissipation for a given application prior to selecting package type. Power dissipation may be calculated:

$$PD = 3 \times \left( V_{S} \times I_{SMAX} + V_{S} \times \frac{\Delta V_{O}}{R_{LD}} \right)$$

(EQ. 1)

where:

- $V_S$  is the total power supply to the EL4543 (from  $V_S$ + to  $V_S$ -)

- I<sub>SMAX</sub> = Maximum quiescent supply current per channel

- $\Delta V_{O}$  = Maximum differential output voltage of the application

- R<sub>LD</sub> = Differential load resistance

- I<sub>LOAD</sub> = Load current

Having obtained the application's power dissipation, the maximum junction temperature can be calculated:

$$T_{JMAX} = T_{MAX} + \Theta_{JA} \times PD$$

(EQ. 2)

where:

- T<sub>JMAX</sub> is the maximum junction temperature (125°C)

- T<sub>MAX</sub> is the maximum ambient operating temperature

- PD is the power dissipation calculated above

- $\theta_{JA}$  is the thermal resistance, junction to ambient, of the application (package + PCB combination). Refer to the Package Power Dissipation curves.

- Note:

For the QFN package, the thermal pad is internally connected to VS- and may only be grounded in applications where a single supply is used and VS- is returned to ground. In applications where VS- is tied to a negative voltage the thermal pad must also be connected to the same negative voltage.

See Technical Bulletin 389 (http://www.intersil.com/data/tb/TB389.pdf) for additional QFN PCB layout information.

# Application Circuit

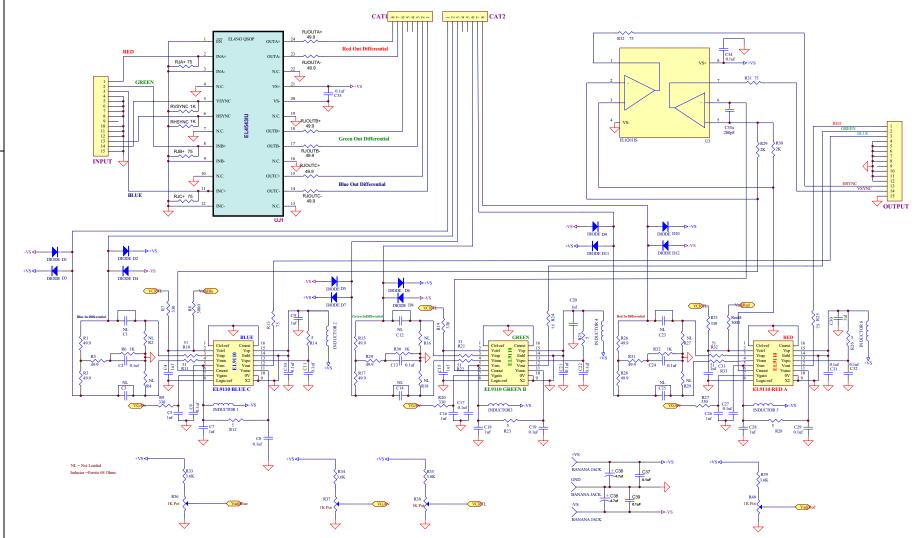

# Video Transmission Along CAT5 Cable

VGA input RGB plus sync is connected with 75 $\Omega$  termination to the inputs of the EL4543. Single-ended RGB video is converted to differential mode signals with H<sub>SYNC</sub> and V<sub>SYNC</sub> encoded on the common-mode of the three differential signals, respectively. The 50 $\Omega$  output-terminated EL4543 drives the differential RGB with sync encoded common-mode to CAT5 twisted pair cables. Note this system, without signal frequency equalization, will satisfactorily transmit along up to 200ft of CAT5 twisted-pair. For longer cable lengths, frequency and gain equalization to compensate for signal degradation is recommended (EL9110) and a delay line technology (EL9115) to adjust for phase mismatch between signals at the receiving end.

# EL4543 and EL9110 Sync Extraction

EL4543

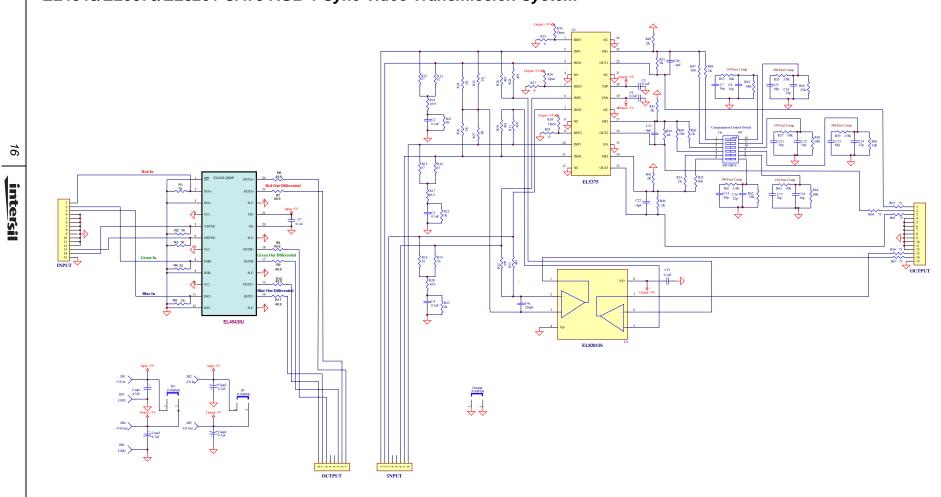

# *EL4543/EL5375/EL8201 CAT5 RGB* + Sync *Video Transmission System*

Introducing a low cost turn-key system for transmitting component video over short to moderate CAT5 cable lengths (1 to 500 feet) with selectable cable loss and skew compensation. Using only 3 of the 4 pairs in standard CAT5 the 4<sup>th</sup> pair is available for audio, function control or data transmission; an additional benefit.

RGB video plus sync (5 channels) is received at the VGA terminal and presented single ended to the EL4543. The EL4543 converts single ended RGB into fully differential signals on three twisted pairs. Sync is encoded on the three RGB differential signals as differential common mode and then drives the differential signals with encoded sync through CAT5 cable. The common mode of the signals is extracted from the differential signals with a passive network of resistors and passed to the EL8201 for sync decoding. The differential signal is passed directly to the EL5375 where it is amplified, converted back into single ended format. Signal attenuation occurs in all transmission lines as a function of increasing cable length; this application system utilizes individual channel 2-pole compensation for cable lengths of 150, 300 and 500 feet. Additionally, the compensation network can be manipulated to provide some

measure of cable prop delay skew compensation for slight differences in cable lengths between CAT5 pairs. Cable skew can best be done around the 300ft range by under compensating the shortest color pair (color on the left side of a vertical line) and over compensate the longest color pair (color on the right side of a vertical line). Around 450ft only the shortest color pair can be under compensated.

The board for the driver and receiver should use strip lines or strip line waveguides for the inputs and outputs of the drivers and receivers. The  $75\Omega$  input and output strip lines waveguide on 0.06 inch epoxy board with ground back plain should be 0.016 inch wide with 0.01 inch space to ground area around them. The differential pair strip line waveguides should be two 0.045 inch  $50\Omega$  lines spaced 0.01 inch apart and spaced 0.01 inch to ground area around them. This is a general guide and size values may very for many reasons.

The receiver feedback and gain resistor network which goes directly to the minus input should be connected very close with minimal trace length and minimal capacitance to ground. The ground plane on the backside of the board, in back of these resistors and the minus input pin should be removed as well.

# EL4543/EL5375/EL8201 CAT5 RGB + Sync Video Transmission System

# **Package Outline Drawing**

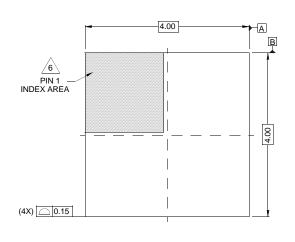

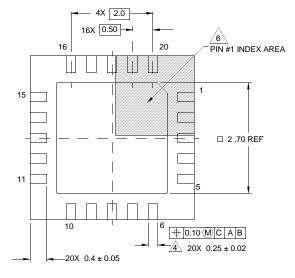

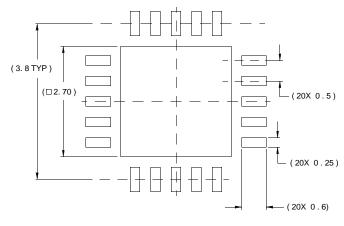

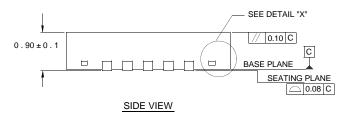

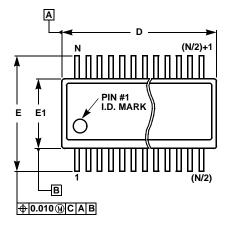

# L20.4x4B

20 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 1, 11/06

TOP VIEW

TYPICAL RECOMMENDED LAND PATTERN

NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

# EL4543

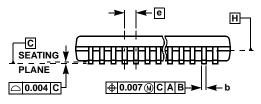

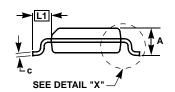

# Quarter Size Outline Plastic Packages Family (QSOP)

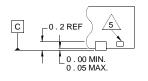

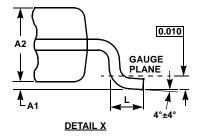

## **MDP0040**

QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

|             | INCHES |        |        |           |       |  |

|-------------|--------|--------|--------|-----------|-------|--|

| SYMBOL      | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES |  |

| А           | 0.068  | 0.068  | 0.068  | Max.      | -     |  |

| A1          | 0.006  | 0.006  | 0.006  | ±0.002    | -     |  |

| A2          | 0.056  | 0.056  | 0.056  | ±0.004    | -     |  |

| b           | 0.010  | 0.010  | 0.010  | ±0.002    | -     |  |

| с           | 0.008  | 0.008  | 0.008  | ±0.001    | -     |  |

| D           | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3  |  |

| E           | 0.236  | 0.236  | 0.236  | ±0.008    | -     |  |

| E1          | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3  |  |

| е           | 0.025  | 0.025  | 0.025  | Basic     | -     |  |

| L           | 0.025  | 0.025  | 0.025  | ±0.009    | -     |  |

| L1          | 0.041  | 0.041  | 0.041  | Basic     | -     |  |

| N           | 16     | 24     | 28     | Reference | -     |  |

| Rev. F 2/07 |        |        |        |           |       |  |

NOTES:

1. Plastic or metal protrusions of 0.006" maximum per side are not included.

2. Plastic interlead protrusions of 0.010" maximum per side are not included.

3. Dimensions "D" and "E1" are measured at Datum Plane "H".

4. Dimensioning and tolerancing per ASME Y14.5M-1994.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com