**♦**STRUCTURE Silicon Monolithic Integrated Circuit **♦PRODUCT** 4K×8 bit Electrically Erasable PROM

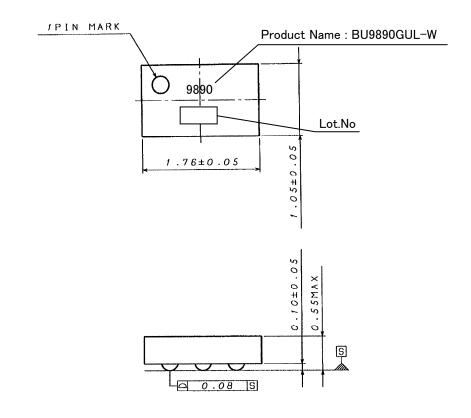

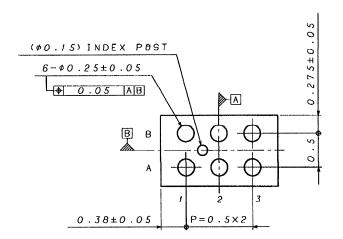

**♦PART NUMBER** BU9890GUL-W ♦ PHYSICAL DIMENSION Fig.-1(VCSP50L1)

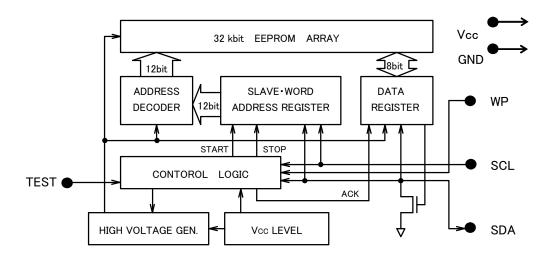

**♦BLOCK DIAGRAM** Fig.-2

♦USE General purpose

**♦FEATURES** •4K words × 8 bits architecture serial EEPROM

•Wide operating voltage range (1.7V ~ 3.6V)

Two wire serial interface

· Self-timed write cycle with automatic erase

•32 byte Page Write mode •Low power consumption。

> Write (3.3V) : 0.6mA (Typ.) (3.6V) : 0.6mA (Typ.) Read Standby (3.6V) :  $0.1 \mu$  A (Typ.)

DATA security

Write protect feature (WP pin) Inhibit to WRITE at low VCC

•WLCSP 6pin package

· High reliability fine pattern CMOS technology • Endurance : 100,000 erase/write cycles • Data retention : 40 years

•Filtered inputs in SCL•SDA for noise suppression

·Initial data FFh in all address

•Pull-up resistor inputs in SCL•SDA

### ♦ ABSOLUTE MAXIMUM RATING (Ta=25°C

| Parameter             | Symbol | Rating          | Unit |

|-----------------------|--------|-----------------|------|

| Supply Voltage        | Vcc    | <b>-0.3∼6.5</b> | ٧    |

| Power Dissipation     | Pd     | 220 *1          | mW   |

| Storage Temperature   | Tstg   | <b>-65∼125</b>  | °C   |

| Operating Temperature | Topr   | <b>-40∼</b> 85  | °C   |

| Terminal Voltage      |        | -0.3∼Vcc+1.0 *2 | ٧    |

<sup>\*1</sup> Degradation is done at 2.2mW/°C(\*1) for operation above 25°C

### ♦ RECOMMENDED OPERATING CONDITION

| Paramete       | r    | Symbol   | Rating  | Unit |  |

|----------------|------|----------|---------|------|--|

| Write          |      | M        | 2.7~3.3 | V    |  |

| Supply Voltage | Read | Vcc      | 1.7~3.6 | V    |  |

| Input Volta    | ge   | $V_{IN}$ | 0~Vcc   | V    |  |

<sup>\*2</sup> Maximum value of Terminal Voltage is below 6.5V.

### ♦DC OPERATING CHARACTERISTICS (Unless otherwise specified Ta=-40~85°C, Vcc=1.7~3.6V)

| DO OPERATING CHARAC    | LEKI2       | HUS (Unic     | ess oth | erwise sp | ecitie | ed 1a=-40~85°C, VCC=1./~3.6V)                                          |  |

|------------------------|-------------|---------------|---------|-----------|--------|------------------------------------------------------------------------|--|

| Parameter              | Symb        | Specification |         |           |        |                                                                        |  |

| Farameter              | ol          | Min.          | Тур.    | Max.      | Unit   | test condition                                                         |  |

| "H" Input Voltage1     | VIH1        | 0.7Vcc        | ı       | Vcc+1.0   | ٧      | 2.5V≦Vcc≦3.6V                                                          |  |

| "L" Input Voltage1     | VIL1        | -0.3          | _       | 0.3Vcc    | ٧      | 2.5V≦Vcc≦3.6V                                                          |  |

| "H" Input Voltage2     | VIH2        | 0.8Vcc        | _       | Vcc+1.0   | ٧      | 1.8V≦Vcc<2.5V                                                          |  |

| "L" Input Voltage2     | VIL2        | -0.3          | -       | 0.2Vcc    | ٧      | 1.8V≦Vcc<2.5V                                                          |  |

| "H" Input Voltage3     | VIH3        | 0.9Vcc        | -       | Vcc+1.0   | ٧      | 1.7V≦Vcc<1.8V                                                          |  |

| "L" Input Voltage3     | VIL3        | -0.3          | ı       | 0.1Vcc    | ٧      | 1.7V≦Vcc<1.8V                                                          |  |

| "L" Output Voltage1    | Vol1        | _             | -       | 0.4       | ٧      | IoL=3.0mA, 2.5V≦Vcc≦3.6V(SDA)                                          |  |

| "L" Output Voltage2    | VOL2        | _             | -       | 0.2       | ٧      | IoL=0.7mA, 1.7V≦Vcc<2.5V(SDA)                                          |  |

| Input Leakage Current  | ĪLΙ         | -1            | _       | 1         | μΑ     | Vin=0V~Vcc, (WP, TEST)                                                 |  |

| Pull-up resistor       | ILI2        | 6             | 10      | 14        | kΩ     | (SCL, SDA)                                                             |  |

| Output Leakage Current | <b>I</b> LO | -1            | ı       | 1         | μΑ     | Vout=0V~Vcc(SDA)                                                       |  |

|                        | Icc1        | -             | -       | 4.1       | mA     | Vcc=3.3V,fscL=400kHz, twn=5ms<br>Byte Write<br>Page Write              |  |

| Operating Current      | ICC2        | -             | _       | 1.7       | mA     | Vcc=3.6V,fscL=400kHz<br>Random Read<br>Current Read<br>Sequential Read |  |

| Standby Current        | Isb         | _             | _       | 2.0       | μΑ     | Vcc=3.6V,SDA,SCL=Vcc<br>WP=GND                                         |  |

O This product is not designed for protection against radioactive rays.

# ♦ MEMORY CELL CHARACTERISTICS(Ta=25°C, Vcc=1.7~3.6V)

| Dayamatay            |         | 11   |      |       |  |

|----------------------|---------|------|------|-------|--|

| Parameter            | Min.    | Тур. | Max. | Unit  |  |

| Write/Erase Cycle *1 | 100,000 | _    | 1    | cycle |  |

| Data Retention *1    | 40      | _    | 1    | year  |  |

\*1:Not 100% TESTED

(UNIT: mm)

Drawing No: EX912-5031

Fig.-1 PHYSICAL DIMENSION (Unit:mm)

### ♦BLOCK DIAGRAM

Fig.-2 BLOCK DIAGRAM

TEST Pin Connect with GND

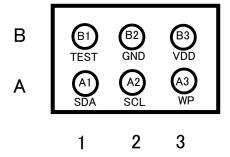

# ♦PIN CONFIGURATION

## **♦PIN NAME**

| Land No. | PIN NAME | I/O                          | FUNCTIONS                                                        |  |  |

|----------|----------|------------------------------|------------------------------------------------------------------|--|--|

| В3       | Vcc      | - Power Supply               |                                                                  |  |  |

| B2       | GND      | - Ground (0V)                |                                                                  |  |  |

| B1       | TEST     | IN TEST Pin Connect with GND |                                                                  |  |  |

| A3       | WP       | IN Write Protect Input       |                                                                  |  |  |

| A2       | SCL      | IN                           | Serial Clock Input                                               |  |  |

| A1       | SDA      | IN/OUT                       | Slave and Word Address,<br>Serial Data Input, Serial Data Output |  |  |

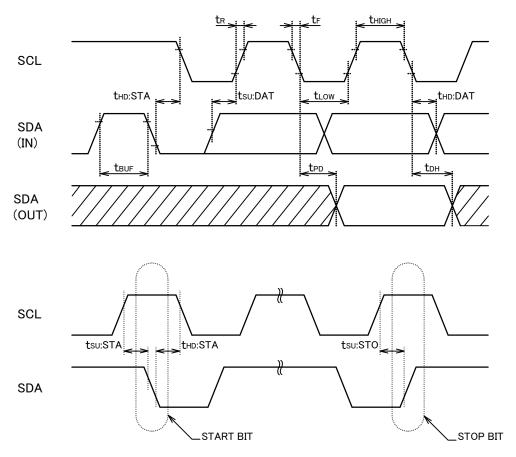

♦AC OPERATING CHARACTERISTICS (Unless otherwise specified Ta=-40~85°C, Vcc=1.7~3.6V)

| C OPERATING CHARACTERISTICS (Uni | Symbol   | FAST-MODE     |      |      | STANDARD-MODE |      |      | Unit |

|----------------------------------|----------|---------------|------|------|---------------|------|------|------|

| Parameter                        |          | 2.5V≦Vcc≦3.6V |      |      | 1.7V≦Vcc≦3.6V |      |      |      |

|                                  |          | Min.          | Тур. | Max. | Min.          | Тур. | Max. |      |

| Clock Frequency                  | fSCL     | _             | _    | 400  | _             | _    | 100  | kHz  |

| Data Clock High Period           | tHIGH    | 0.6           | _    | _    | 4.0           | _    | _    | μs   |

| Data Clock Low Period            | tLOW     | 1.2           | _    | _    | 4.7           | _    | _    | μs   |

| SDA and SCL Rise Time *1         | tR       | -             | _    | 0.3  | -             | _    | 1.0  | μs   |

| SDA and SCL Fall Time *1         | tF       | -             | _    | 0.3  | _             | _    | 0.3  | μs   |

| Start Condition Hold Time        | tHD:STA  | 0.6           | _    | _    | 4.0           | _    | _    | μs   |

| Start Condition Setup Time       | tSU:STA  | 0.6           | _    |      | 4.7           | _    | _    | μs   |

| Input Data Hold Time             | tHD:DAT  | 0             | _    | _    | 0             | _    | _    | ns   |

| Input Data Setup Time            | tSU:DAT  | 100           | _    | _    | 250           | _    | _    | ns   |

| Output Data Delay Time           | tPD      | 0.1           | _    | 0.9  | 0.2           | _    | 3.5  | μs   |

| Output Data Hold Time            | tDH      | 0.1           | _    | _    | 0.2           | _    | _    | μs   |

| Stop Condition Setup Time        | tSU:STO  | 0.6           | _    | _    | 4.7           | _    | _    | μs   |

| Bus Free Time                    | tBUF     | 1.2           | _    | _    | 4.7           | _    | _    | μs   |

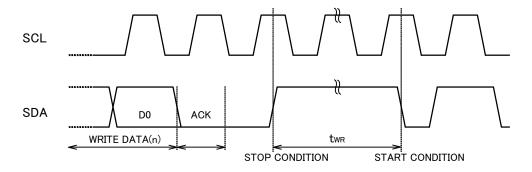

| Write Cycle Time                 | tWR      | _             | _    | 5    | _             | _    | 5    | ms   |

| Noise Spike Width (SDA and SCL)  | tI       | _             | _    | 0.1  | _             | _    | 0.1  | μs   |

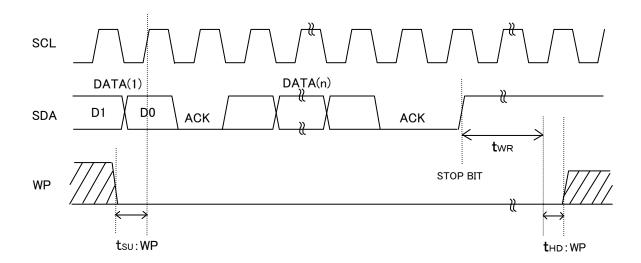

| WP Hold Time                     | tHD:WP   | 0             | _    |      | 0             | _    | _    | ns   |

| WP Setup Time                    | tSU:WP   | 0.1           | _    |      | 0.1           | _    | _    | μs   |

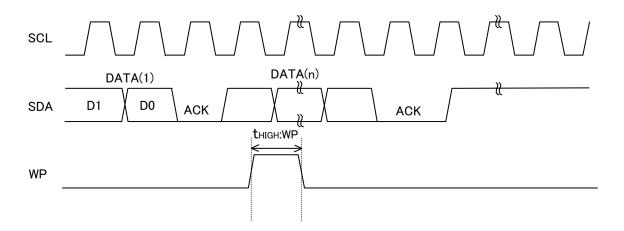

| WP High Period                   | tHIGH:WP | 1.0           | _    | _    | 1.0           | _    | _    | μs   |

\*1:Not 100% TESTED

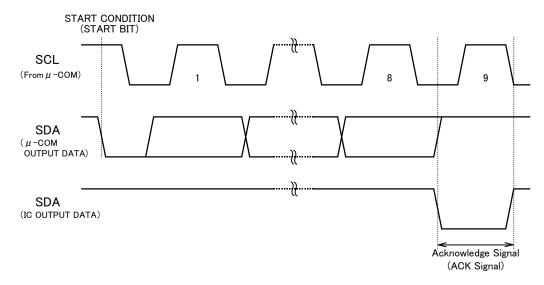

### **♦**SYNCHRONOUS DATA TIMING

Fig.-4 SYNCHRONOUS DATA TIMING

OSDA data is latched into the chip at the rising edge of SCL clock. OOutput date toggles at the falling edge of SCL clock.

### **♦WRITE CYCLE TIMING**

Fig.-5 WRITE CYCLE TIMING

**♦WP TIMING**

Fig.-6(a) WP TIMING OF THE WRITE OPERATION

Fig.-6(b) WP TIMING OF THE WRITE CANCEL OPERATION

OFor the WRITE operation, WP must be "LOW" during the period of time from the rising edge of the clock which takes in D0 of first byte until the end of twr. (See Fig.-6(a))

During this period, WRITE operation is canceled by setting WP "HIGH".( See Fig.-6(b) )

OIn the case of setting WP "HIGH" during two, WRITE operation is stopped in the middle and the data of accessing address is not guaranteed. Please write correct data again in the case.

#### **♦DEVICE OPERATION**

#### OSTART CONDITION (RECOGNITION OF START BIT)

- •All commands are proceeded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH.

- •The device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met.

(See Fig.-4 SYNCHRONOUS DATA TIMING)

### OSTOP CONDITION (RECOGNITION OF STOP BIT)

•All commands must be terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is HIGH.

(See Fig.-4 SYNCHRONOUS DATA TIMING)

#### ONOTICE ABOUT WRITE COMMAND

•In the case that stop condition is not excuted in WRITE mode, transferred data will not be written in a memory.

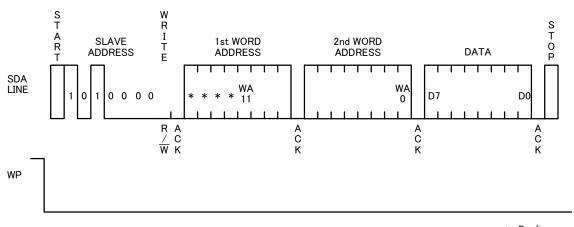

### **ODEVICE ADDRESSING**

- •Following a START condition, the master output the slave address to be accessed.

- •The most significant four bits of the slave address are the "device type indentifier," for this device it is fixed as "1010" and next three bit set to "000".

- •The last bit of the stream  $(R/\overline{W} \cdots READ/\overline{WRITE})$  determines the operation to be performed. When set to "1", a read operation is selected; when set to "0", a write operation is selected.

$R/\overline{W}$  set to "0"  $\cdot$   $\cdot$   $\cdot$   $\cdot$  · · · · · · · WRITE (including word address input of Random Read)  $R/\overline{W}$  set to "1"  $\cdot$  · · · · · · · · · READ

| 1010 | 0 0 | 0 | R∕W |

|------|-----|---|-----|

|------|-----|---|-----|

#### OWRITE PROTECT (WP)

When WP pin set to Vcc(H level), write protect is set for 4,096 words (all address). When WP pin set to GND(L level), it is enable to write 4,096 words (all address). Either control this pin or connect to GND ( or Vcc). It is inhibited from being left unconnected.

#### **OACKNOWLEDGE**

- •Acknowledge is a software convention used to indicate successful data transfers. The transmitter device will release the bus after transmitting eight bits.

- (When inputting the slave address in the write or read operation, transmitter is  $\mu$ -COM. When outputting the data in the read operation, it is this device.)

- •During the ninth clock cycle, the receiver will pull the SDA line LOW to acknowledge that the eight bits of data has been received.

- (When inputting the slave address in the write or read operation, receiver is this device. When outputting the data in the read operation, it is  $\mu$ -COM.)

- •The device will respond with an Acknowledge after recognition of a START condition and its slave address (8bit).

- •In the WRITE mode, the device will respond with an Acknowledge, after the receipt of each subsequent 8-bit word (word address and write data).

- •In the READ mode, the device will transmit eight bit of data, release the SDA line, and monitor the line for an Acknowledge.

- •If an Acknowledge is detected, and no STOP condition is generated by the master, the device will continue to transmit the data.

If an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition before returning to the standby mode.

(See Fig.-7 ACKNOWLEDGE RESPONSE FROM RECEIVER)

Fig.-7 ACKNOWLEDGE RESPONSE FROM RECEIVER

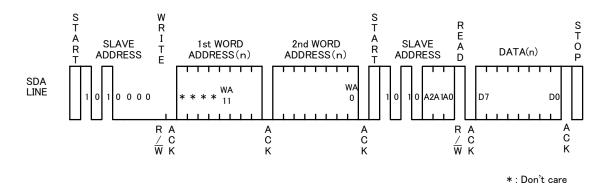

\* : Don't care

Fig.-8 BYTE WRITE CYCLE TIMING

OBy using this command, the data is programed into the indicated word address. OWhen the master generates a STOP condition, the device begins the internal write cycle to the nonvolatile memory array.

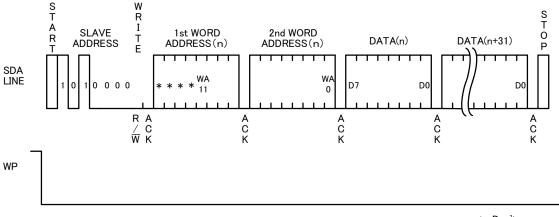

\* : Don't care

Fig.-9 PAGE WRITE CYCLE TIMING

- OThis device is capable of thirty-two byte Page Write operation.

- OWhen two or more byte data are inputted, the five low order address(WA4~WA0) bits are in ternally incremented by one after the receipt of each word. The seven higher order bits of the address(WA4~WA0) remain constant.

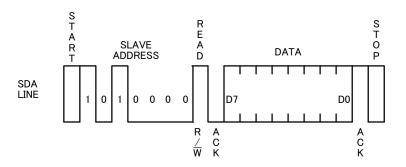

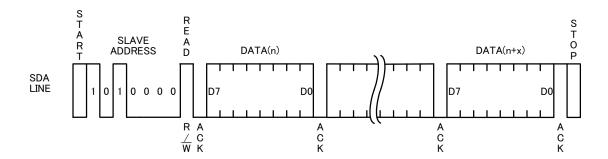

Fig.-10 CURRENT READ CYCLE TIMING

O In case that the previous operation is Random or Current Read (which includes Sequential Read respectively), the internal address counter is increased by one from the last accessed address (n). Thus Current Read outputs the data of the next word address (n+1).

If the last command is Byte or Page Write, the internal address counter stays at the last address (n). Thus Current Read outputs the data of the word address (n).

Olf an Acknowledge is detected, and no STOP condition is generated by the master ( $\mu$ -COM), the device will continue to transmit the data. [It can transmit all data (32kbit 4096word)] Olf an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition before returning to the standby mode.

NOTE) If an Acknowledge is detected with "Low" level, not "High" level, command will become Sequential Read. So the device transmits the next data, Read is not terminated. In the case of terminating Read, input Acknowledge with "High" always, then input stop condition.

Fig.-11 RANDOM READ CYCLE TIMING

ORandom Read operation allows the master to access any memory location indicated word address.

Olf an Acknowledge is detected, and no STOP condition is generated by the master ( $\mu$ -COM), the device will continue to transmit the data. [It can transmit all data (32kbit 4096word)] Olf an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition before returning to the standby mode.

NOTE) If an Acknowledge is detected with "Low" level, not "High" level, command will become Sequential Read. So the device transmits the next data, Read is not terminated. In the case of terminating Read, input Acknowledge with "High" always, then input stop condition.

Fig.-12 SEQUENTIAL READ CYCLE TIMING ( Current Read )

OOIf an Acknowledge is detected, and no STOP condition is generated by the master ( $\mu$ -CO M), the device will continue to transmit the data. [It can transmit all data (32kbit 4096word)] OIf an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition before returning to the standby mode.

OThe Sequential Read operation can be performed with both Current Read and Random Read.

NOTE) If an Acknowledge is detected with "Low" level, not "High" level, command will become Sequential Read. So the device transmits the next data, Read is not terminated. In the case of terminating Read, input Acknowledge with "High" always, then input stop condition.

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact us.

# **ROHM Customer Support System**

http://www.rohm.com/contact/